Kétlépcsős T flip-flop - studopediya

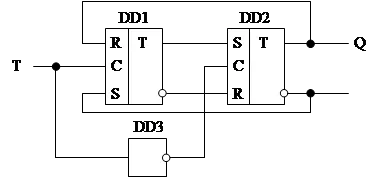

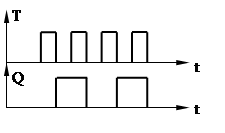

A kétlépcsős ravaszt, amely két szereplő sorozat reteszt visszacsatolások, az „új” információkat tárolnak az első flip-flop, miközben a „régi” információ a második. Amikor az „új” információ tárolva, és egy aktív jelet kivesszük bemeneti TS törli a „régi” információs és felülírja az „új” információ a második ravaszt. Reakcióvázlat kétlépcsős T-flip-flop, épített két szinkron RS-flip-flop, és annak működését időzítési diagramja ábrán látható. 5.9.

Ábra. 5.9. Reakcióvázlat (a) és a időzítési diagramja (b) egy kétlépcsős T-flip-flop

Egy kétfokozatú T flip-flop két flip-flop - master és a slave DD1 DD2. Hogy megszüntesse generáló áramkört módú óra bemenetei flip-flop tartalmazza keresztül DD3 inverter, azaz a szinkronizálás kapunk fordított logikai szintű. Visszacsatolások közvetlen hozzáférést biztosít a bemeneti DD2 R DD1 és DD2 fordított kimenet S DD1 lehet létrehozni a bemeneti jel megfelelő algoritmus dolgozik T flip-flop. Megjegyezzük, hogy a kimenet a kétlépcsős T flip-flop után jelenik eltávolítása aktív bemeneti jel T, amikor az információ felülírja az első flip-flop a második. Ez biztosítja a normál működés (nincs impulzus generáció) az áramkörben visszacsatolással.

Megkülönböztetni a két szakaszból álló ravaszt egy egyfokozatú, a feltételes grafikus kép elhelyezett kettős betű (TT).

5.6. A kétlépcsős egyidejű JK -trigger

A megkülönböztető jegye a JK -triggera az, hogy még nem tiltott kombinációk bemenetén az információkat is. JK -triggera munka leírja átmenet táblázat (5.5 táblázat), amelyben az aktív jel tekinthető logikai 1. Az aktív J bemeneti trigger jelet kapcsol az állam Q = 1, és K bemenet - Q = 0.

Táblázat átmenetek JK -triggera

Ábra. 5.10. Blokkvázlat JK -triggera

Mint látható a diagram, a bemenetek elemek 3I DDR3 vagy DD4 DD2 mellékelt a ravaszt kimeneti jel logikai 0 és logikai egységet. Ezért a bemenetek J és K lehet bármilyen jelet, de S és R DD1 bemenetek egyidejűleg két aktív jel nem érkezik.

JK -trigger egyetemes. Ezen az alapon lehet létrehozni bármilyen flip-flop áramkör. Ábra. 5.11 ábra a végrehajtása során a korábban tekinthető JK flip-flop -triggere.

Ábra. 5.11. Végrehajtása kiváltó alapján JK -triggera:

és - a szinkron RS-FF; b - D-flip-flop; a - a T-flip-flop

Egy sor TTL JK -trigger készült K155TV1 chip, CMOS sorozat - K561TV1 és K176TV1, ez minden egyetlen chip a sorozatban. Ez annak köszönhető, hogy alacsony az igény flip-flop statikus vezérlő használható automatizálási és távirányító rendszerek.